深度了解 DDR5 RDIMM VLP 的节省空间优势

隨著高效能運算(HPC)需求日益增長,以及數據資料與產業應用的日趨複雜,在有限空間下的終端應用場域,也逐漸受到重視。在這樣的背景下,DDR5 RDIMM VLP 記憶體模組便扮演了關鍵角色。本文將帶您深入了解 DDR5 RDIMM VLP,從技術上的挑戰與突破,到它的優勢與效益。

DDR5 RDIMM VLP 的常见应用场景

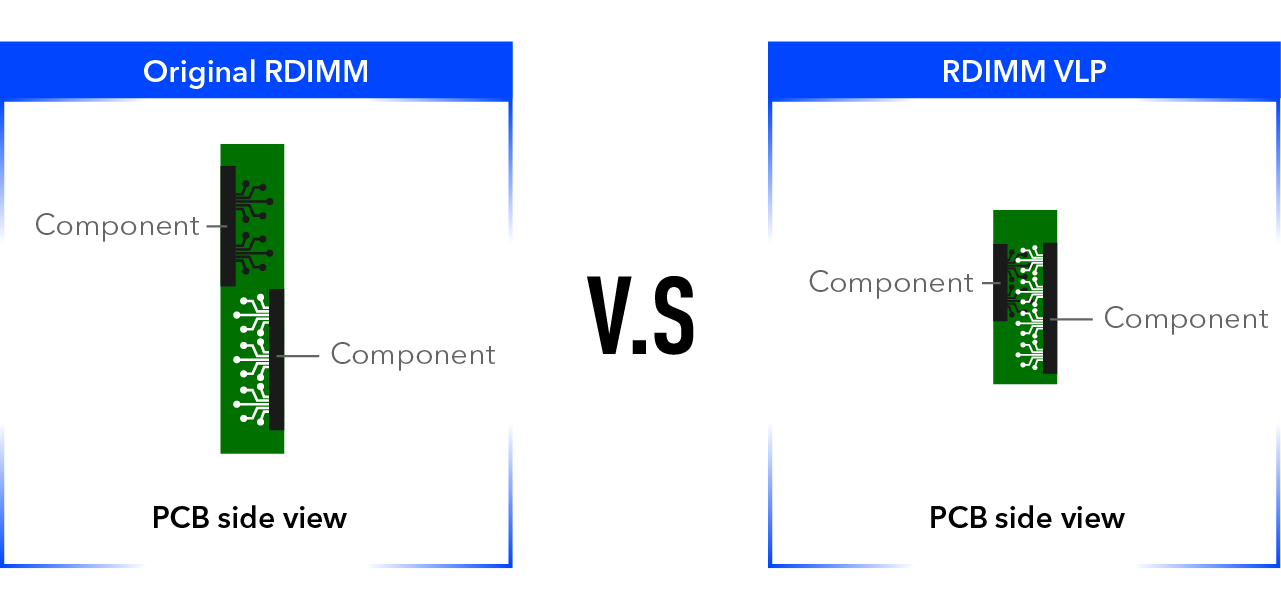

DDR5 RDIMM VLP 记忆体模组广泛应用于各种运算环境中,特别是在系统空间有限的伺服器架构中,尤能展现其优势。这类模组透过缩减电路板(PCB)的实际高度,有效减少体积,同时保有效能与稳定性。不论是部署在紧凑型刀锋伺服器(blade servers),还是其他空间受限的系统设备中,DDR5 RDIMM VLP 都能提升伺服器的密度与运作效率。

DDR5 RDIMM VLP 的优势

DDR5 RDIMM VLP 模组具备多项关键优势,使其在空间受限的伺服器架设环境中,成为不可或缺的记忆体解决方案。

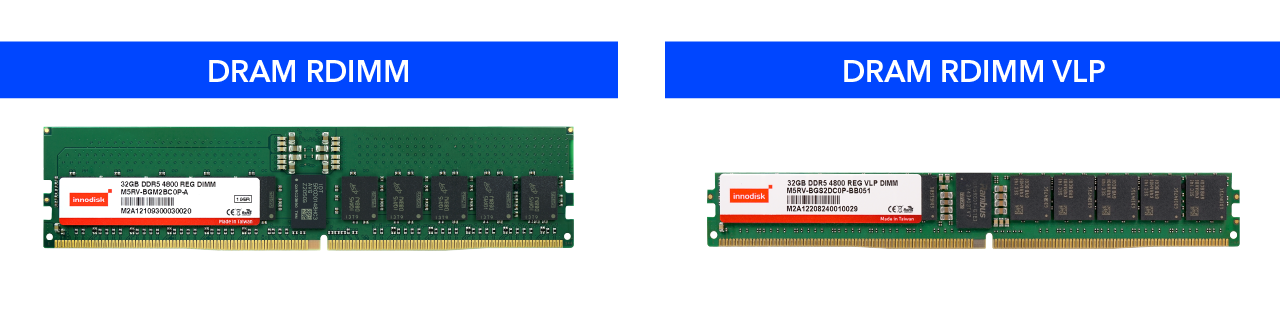

1. 更小的实体体积

VLP 模组具备更小的规格尺寸,让伺服器能够配置更高密度的记忆体,进一步在有限的空间内扩充容量,同时不影响整体效能与稳定性。

2. 优异的散热效能与设计弹性

DDR5 RDIMM VLP 采用精巧设计,使伺服器内部配置更具弹性。由于记忆体模组时常紧邻 CPU、GPU 等容易产生热能的元件,此时, DDR5 RDIMM VLP 的小尺寸设计,便能促进气流循环,有效提升散热效率、降低系统温度,进而提升系统稳定性与长时间运作的可靠性。此外,节省下的空间更能创造系统设计的灵活性,协助企业最佳化伺服器部署,实现高效率与可扩充性兼备的解决方案。

3. 降低系統整體功耗

DDR5 RDIMM VLP 不仅强化了散热效能,也进一步降低整体系统功耗。藉由提升被动散热的效率,能够减少风扇与其他主动散热机制的依赖,进而降低电源利用,创造更具永续性与可靠性的伺服器架构。

DDR5 RDIMM VLP 模组可说是现代化伺服器架构的关键零组件,让高密度记忆体能够无缝整合至空间有限的资料中心,优化系统部署效率与扩充性。

产品开发的技术挑战

为全球领先的工控记忆体模组品牌,宜鼎在开发 DDR5 RDIMM VLP 模组的过程中,仍面临各式技术挑战。其中一大关键在于如何确保新一代 DDR5 记忆体元件能够与各式各样的主机板有效相容。此外,在缩小模组尺寸的同时,仍需符合业界对于效能与稳定性的严格标准,也是技术上的一大考验。然而,透过严谨的测试流程与创新的设计思维,我们成功克服了这些挑战,并推出具备高效能与稳定性的 DDR5 RDIMM VLP 记忆体模组。

技术创新与突破

为了解决上述技术难题,我们采取多项策略,确保模组能兼顾最佳效能与可靠性。在整体开发过程中,我们持续进行测试与验证,特别针对 DDR5 记忆体元件的相容性,规划出三大核心验证项目:

- PMIC 电源完整性测试(Power Integrity, PI)

- PD Hub 讯号完整性测试(Signal Integrity, SI)

- Rank Margin Test(RMT)测试

透过细致的分析每个零组件的稳定性验证结果,我们得以设计并开发出最高标准的记忆体模组。

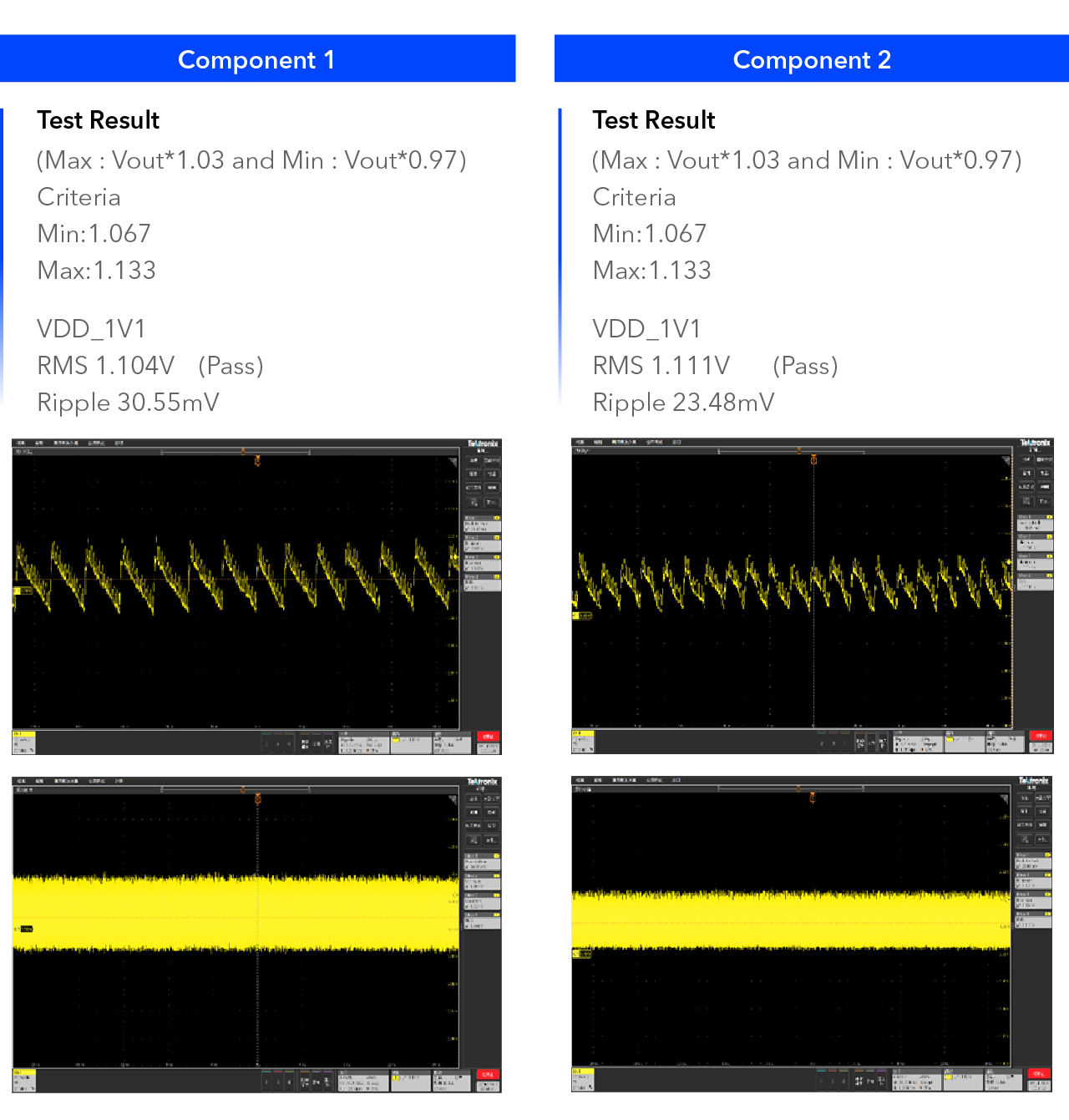

PMIC 电源完整性(PI)测试:确保讯号稳定性

PMIC(电源管理积体电路)在 DRAM 模组中扮演电力分配与稳定电压的角色。当电压由 12V 降至 1.1V,其过程中产生的电压波动与杂讯,可能影响 DRAM 模组的效能与稳定性。即使这些元件符合 JEDEC 标准,不同主机板与零组件搭配下的 PMIC 表现与抗杂讯能力,仍可能有所不同。

为了验证供电稳定性,我们针对来自多家供应商的 PMIC 进行电源完整性(PI)测试。稳定的电源供应,对于讯号的传输与接收至关重要。例如,在下图中可见,元件 A 的电源纹波杂讯明显高于元件 B。过高的纹波杂讯(Ripple Noise)与电压振幅,会导致电源供应不稳定,进而影响整体记忆体模组效能。

因此,较低的纹波杂讯代表更佳的讯号稳定性,使得元件 B 成为在高效能环境下更可靠的选择,有助于维持 DRAM 模组的稳定运作。

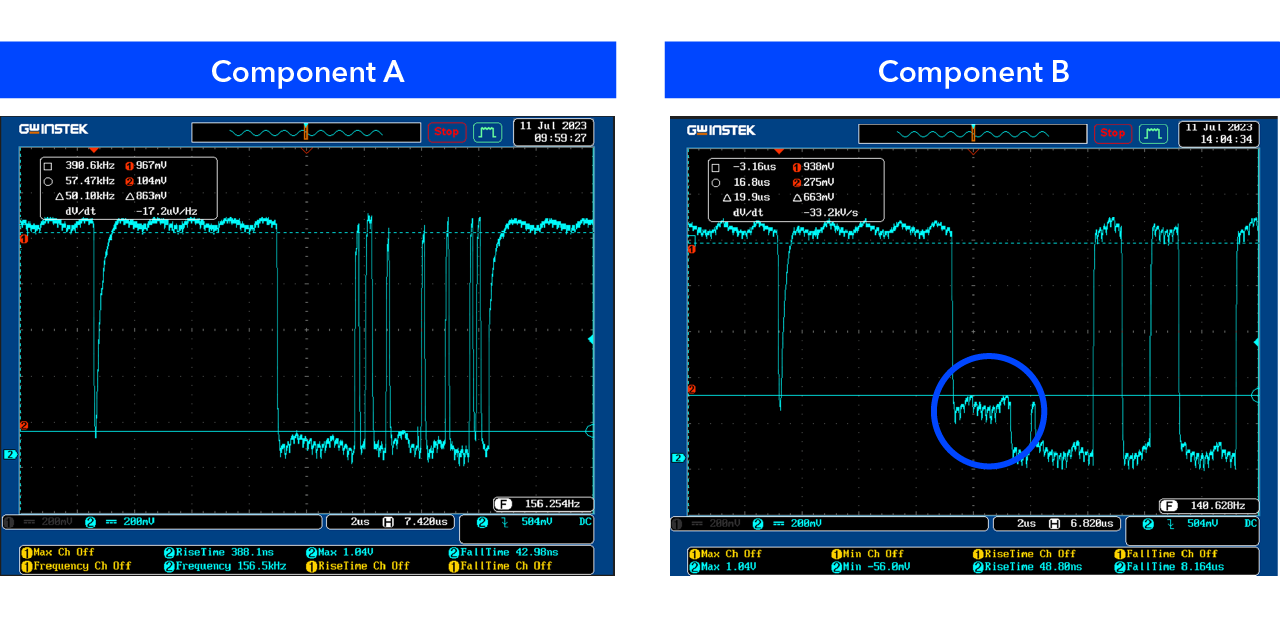

SPD Hub 讯号完整性(SI)测试:确保系统稳定运作

在高速资料传输环境中,传输线、DRAM IC、PCB 电路板等各项元素,都可能对讯号传输产生干扰,因此过程中的「讯号完整性(Signal Integrity, SI)」至关重要。为了确保资料准确传输,我们透过「示波器(Oscilloscope)」对 SPD Hub 的 I2C / I3C 讯号进行量测与分析。如下图所示,测试结果显示:元件 B 偶尔出现讯号振幅偏低的现象,这种不稳定可能会造成资料错误或不一致。

相较之下,元件 A 在时序与振幅上表现稳定,可作为维持资料传输可靠性与系统稳定性的参考指标。因此,选用具备稳定测试表现的 SPD Hub 元件,对于 DRAM 模组在高频、高负载环境下的稳定运作具有决定性影响。

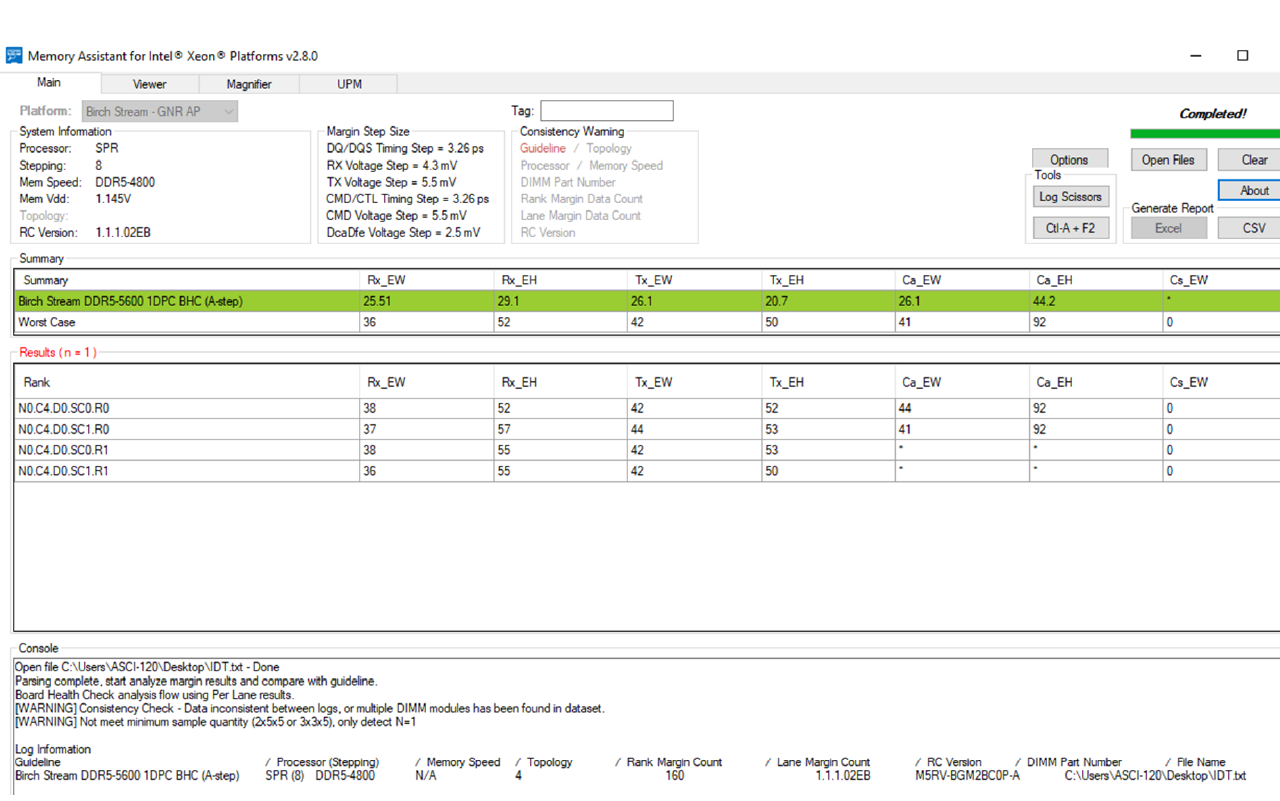

RMT 测试:验证记忆体与主机板相容性

Intel RMT(Rank Margin Test)测试是评估记忆体与主机板之间讯号品质与相容性的业界标准方法,藉由验证模组时序与电压的容忍范围,确保模组在系统平台上的稳定运作。

元件配置对讯号干扰的影响

除了测试单一零组件的讯号表现,我们也深入研究元件排列方式与 PCB 材质对讯号稳定性的影响。由于RDIMM VLP 模组的 PCB 面积缩小约 40%,因此一定程度压缩了各项零组件之间的距离,并可能因此增加讯号干扰的风险,并影响整体讯号稳定性。

PCB 设计优化:降低干扰、提升讯号品质

为了减少讯号干扰,我们采取了两项策略:重新设计走线方式、采用多层 PCB 结构。其中,增加 PCB 层数可降低介电常数(DK)、强化讯号稳定性。宜鼎的 DDR5 RDIMM VLP 采用高密度互连(HDI)PCB 制程,有效提升元件隔离并降低干扰风险。

透过上述完整严谨的验证测试流程,我们能够挖掘并修正各式潜在风险,并借以打造出高品质与高效能的 DDR5 RDIMM VLP 內存模组。

结语

DDR5 RDIMM VLP 內存模组为现今伺服器面临的空间限制,提供了一个创新且高效的解决方案。凭借更小的模组尺寸与优异的散热能力,宜鼎 DDR5 RDIMM VLP 內存模组能让企业在有限空间内,大幅提升记忆体容量,并在严谨的测试流程下,确保各式零组件组合的稳定性,展现绝佳稳定性与效能。

随着企业对伺服器效能与扩充性的需求日益提升,DDR5 RDIMM VLP 模组正成为资料中心空间优化的关键利器,展现其优异的部署弹性。